# University of South Carolina **Scholar Commons**

Theses and Dissertations

8-9-2014

# MEMORY INTERFACE SYNTHESIS FOR FPGA-BASED COMPUTING

Zheming Jin University of South Carolina - Columbia

Follow this and additional works at: http://scholarcommons.sc.edu/etd

#### Recommended Citation

This Open Access Dissertation is brought to you for free and open access by Scholar Commons. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of Scholar Commons. For more information, please contact SCHOLARC@mailbox.sc.edu.

#### MEMORY INTERFACE SYNTHESIS FOR FPGA-BASED COMPUTING

by

#### Zheming Jin

Bachelor of Science Huaihai Institute of Technology, 2005

> Master of Science Shanghai University, 2008

Submitted in Partial Fulfillment of the Requirements

For the Degree of Doctor of Philosophy in

Computer Science and Engineering

College of Engineering and Computing

University of South Carolina

2014

Accepted by:

Jason D. Bakos, Major Professor

Duncan A. Buell, Committee Member

Manton M. Matthews, Committee Member

Song Wang, Committee Member

Enrico Santi, External Examiner

Lacy Ford, Vice Provost and Dean of Graduate Studies

© Copyright by Zheming Jin, 2014 All Rights Reserved.

#### ACKNOWLEDGEMENTS

I express my gratitude to my advisor Dr. Bakos for his study and research guidance and financial support. He goes to town so we knock on wood. I also remember my advisor at Shanghai University. Many years ago, a little friend said that an advisor should be your mentor, in the past, now, and in the future. In addition, I acknowledge the committee members' reviews and comments, which better the contents of the dissertation.

It is pleasant to know about and learn from my lab mates, Tiffany, Krishna, Yan, Ibriham, Fan, Yang and Ivan. Some of them have graduated while others are going to complete the study. Impressed by their various interests in food, gadgets, technology, politics and religion, I am also thankful for their help and advice.

Finally, I express my gratitude to my parents!

#### **ABSTRACT**

This dissertation describes a methodology for the generation of a custom memory interface and associated direct memory access (DMA) controller for FPGA-based kernels that have a regular access pattern. The interface provides explicit support for the following features: (1) memory latency hiding, (2) static access scheduling, and (3) data reuse. The target platform is a multi-FPGA platform, the Convey HC-1, which has an advanced memory system that presents the user logic with three critical design challenges: the memory system itself does not perform caching or prefetching, memory operations are arbitrarily reordered, and the memory performance depends on the access order provided by the user logic. The objective of the interface is to reconcile the three problems described above and maximize overall interface performance. This dissertation proposes three memory access orders, explores buffering and blocking techniques, and exploits data reuse for the synthesis of custom memory interfaces for specific types of kernels. We evaluate our techniques with two types of benchmark kernels: matrix-vector multiplication and 6- and 27-point stencil operations. Experimental results show the proposed memory interface designs that combine memory latency hiding, access scheduling and data reuse achieve an overall performance speedup of 1.6 for matrix-vector multiplication, 2.2 for a 6-point stencil, and 9.5 for a 27-point stencil as compared to using a na we memory interface.

## TABLE OF CONTENTS

| ACKNOWLEDGEMENTS                                       | iii |

|--------------------------------------------------------|-----|

| ABSTRACT                                               | iv  |

| LIST OF TABLES                                         | vii |

| LIST OF FIGURES                                        | ix  |

| CHAPTER 1 INTRODUCTION                                 | 1   |

| 1.1 Memory Performance                                 | 2   |

| 1.2 OVERVIEW OF DISSERTATION                           | 4   |

| CHAPTER 2 BACKGROUND                                   | 7   |

| 2.1 High-performance Reconfigurable Computing          | 7   |

| 2.2 DYNAMIC RANDOM ACCESS MEMORY                       | 9   |

| 2.3 CONVEY HC-1 MEMORY SYSTEM                          | 13  |

| 2.4 MEMORY ACCESS ORDERING ON THE CONVEY HC-1          | 15  |

| 2.5 MEMORY LATENCY HIDING ON THE CONVEY HC-1           | 16  |

| 2.6 Data Reuse on the Convey HC-1                      | 21  |

| 2.7 Buffering for Memory Latency Hiding and Data Reuse | 22  |

| 2.8 PERFORMANCE MEASUREMENT                            | 22  |

| CHAPTER 3 RELATED WORK                                 | 25  |

| 3.1 THE CONVEY HC-1 SYSTEM                             | 25  |

| 3.2 Memory Access Scheduling                           | 26  |

| 3.3 Memory Latency Hiding                              | 28  |

| 3.4 Data I     | Reuse                                               | 29 |

|----------------|-----------------------------------------------------|----|

| 3.5 3D STE     | ENCIL                                               | 31 |

| CHAPTER 4 PREL | IMINARY RESULTS                                     | 33 |

| 4.1 IMPACT     | T OF DRAM SCHEDULING                                | 33 |

| 4.2 IMPACT     | T OF DOUBLE BUFFERING ON MEMORY LATENCY HIDING      | 36 |

| 4.3 IMPACT     | T OF THE LOOP AND ARRAY ACCESS ORDERS               | 37 |

| 4.4 Data I     | REUSE ANALYSIS OF 3D STENCIL                        | 40 |

| 4.5 BANDV      | VIDTH CHARACTERISTICS OF 3D STENCIL                 | 42 |

| 4.6 Concl      | .USION                                              | 43 |

| CHAPTER 5 MEM  | ORY INTERFACE DESIGNS ON THE CONVEY HC-1            | 45 |

| 5.1 STENCE     | IL                                                  | 45 |

| 5.2 Matri      | X VECTOR MULTIPLICATION                             | 59 |

| 5.3 Concl      | USION                                               | 64 |

| CHAPTER 6 EXPE | ERIMENTAL RESULTS                                   | 66 |

| 6.1 Perfoi     | RMANCE IMPACT OF THE LOOP AND ARRAY ORDERS          | 66 |

| 6.2 Perfoi     | RMANCE IMPACT OF PROPOSED 3D STENCIL KERNEL DESIGNS | 74 |

| 6.3 Perfoi     | RMANCE IMPACT OF MVM DESIGNS WITHOUT DATA REUSE     | 80 |

| 6.4 Perfoi     | RMANCE IMPACT OF PROPOSED MVM DESIGNS               | 85 |

| 6.5 Resou      | RCE UTILIZATION                                     | 87 |

| 6.6 DISCUS     | SSION OF EXPERIMENTAL RESULTS                       | 88 |

| CHAPTER 7 CONG | CLUSION                                             | 91 |

|                |                                                     |    |

## LIST OF TABLES

| Table 2.1 Divisions of memory address fields                                         | 14 |

|--------------------------------------------------------------------------------------|----|

| Table 2.2 Memory operations of read reorder buffer                                   | 20 |

| Table 4.1 DRAM controller efficiency test with 120 access orders                     | 34 |

| Table 4.2 Memory interface stall rate using double buffering                         | 38 |

| Table 4.3 DRAM controller efficiency of 6-point 3D stencil                           | 39 |

| Table 4.4 Data reuse rate of 6-point 3D stencil                                      | 41 |

| Table 4.5 Data reuse rate of 27-point 3D stencil                                     | 41 |

| Table 5.1 Reuse rates of using the loop, array and numerical orders                  | 52 |

| Table 6.1 Results of proposed 6-point stencil design (K-dimension partition)         | 75 |

| Table 6.2 Results of proposed 6-point stencil design (J-dimension partition)         | 76 |

| Table 6.3 Results of proposed 6-point stencil design (I-dimension partition)         | 77 |

| Table 6.4 Comparison of the ideal and actual speedup in proposed 3D 6-point stencil  | 77 |

| Table 6.5 Results of proposed 27-point stencil design (K-dimension partition)        | 79 |

| Table 6.6 Comparison of the ideal and actual speedup in proposed 3D 27-point stencil | 79 |

| Table 6.7 Interface efficiency (no data reuse and row-major)                         | 82 |

| Table 6.8 Interface efficiency (no data reuse and column-major)                      | 82 |

| Table 6.9 DRAM controller efficiency (no data reuse and row-major)                   | 83 |

| Table 6.10 DRAM controller efficiency (no data reuse and column-major)               | 83 |

| Table 6.11 Runtime (no data reuse and row-major)                                     | 83 |

| Table 6.12 Runtime (no data reuse and column-major)                                  | 83 |

| Table 6.13 Interface efficiency (Data reuse)                                    | 85 |

|---------------------------------------------------------------------------------|----|

| Table 6.14 DRAM controller efficiency (Data reuse)                              | 85 |

| Table 6.15 Runtime (Data reuse)                                                 | 86 |

| Table 6.16 Runtime (data reuse) vs. runtime (without data reuse)                | 86 |

| Table 6.17 The ideal speedup and the actual speedup in the proposed MVM designs | 86 |

| Table 6.18 Resource utilization of 6-point and 27-point 3D stencils             | 87 |

| Table 6.19 Resource utilization of MVMs                                         | 88 |

# LIST OF FIGURES

| Figure 2.1 Simplified version of FPGA internal architecture                          | 7  |

|--------------------------------------------------------------------------------------|----|

| Figure 2.2 Convey's hybrid-core computer                                             | 9  |

| Figure 2.3 Modern DRAM organization                                                  | 10 |

| Figure 2.4 Memory access scheduling of eight memory operations                       | 12 |

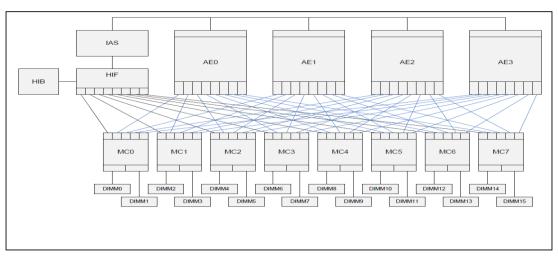

| Figure 2.5 Convey HC-1 memory architecture                                           | 12 |

| Figure 2.6 Memory access orderings on Convey HC-1                                    | 16 |

| Figure 2.7 Double-buffering control FSM                                              | 17 |

| Figure 2.8 Double buffer behaviors and memory interface and pipeline utilization     | 18 |

| Figure 2.9 State transitions of the reorder buffer                                   | 19 |

| Figure 4.1 6-point 3D stencil loop kernel                                            | 37 |

| Figure 4.2 Block diagram of the 6-point 3D stencil for each PE                       | 38 |

| Figure 5.1 6-point and 27-point 3D stencils                                          | 46 |

| Figure 5.2 A 5×5×4 grid with elements numbered numerically                           | 48 |

| Figure 5.3 Block diagram of the proposed 3D 6-point stencil for each PE              | 50 |

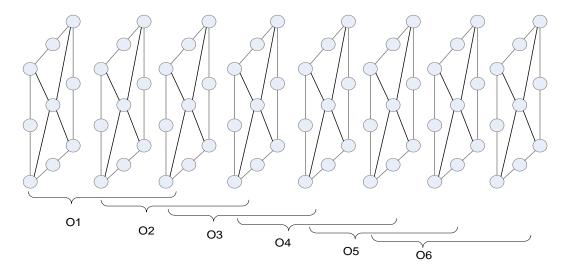

| Figure 5.4 Stencil computation of six output elements in 27-point 3D stencil         | 56 |

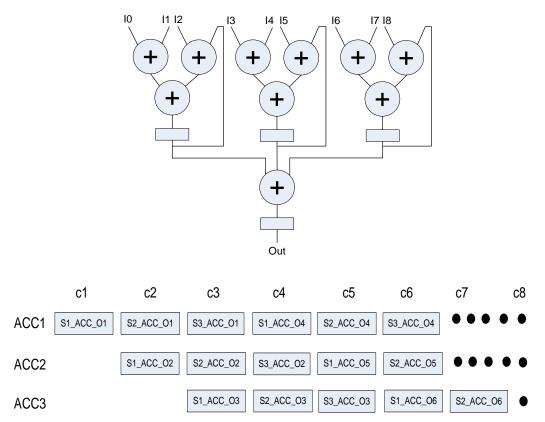

| Figure 5.5 Block diagram of one of the three accumulators which operate in parallel. | 56 |

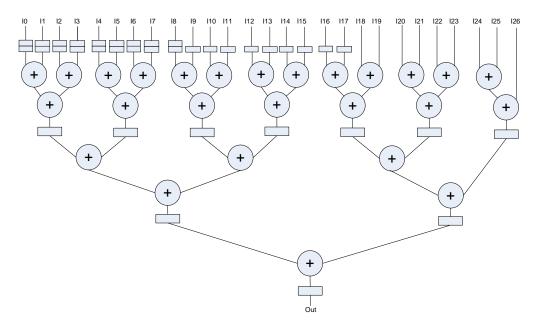

| Figure 5.6 Block diagram of 27-input 64-bit pipelined adder                          | 58 |

| Figure 5.7 The standard algorithm of MVM                                             | 59 |

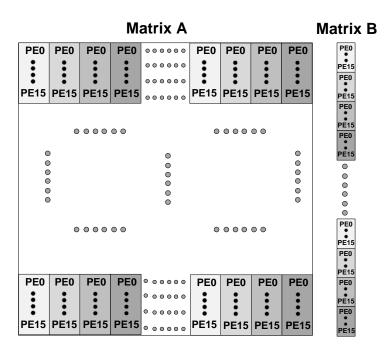

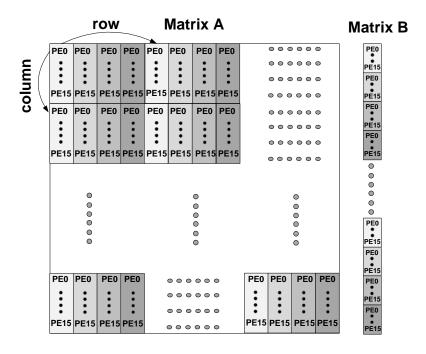

| Figure 5.8 Matrix blocks assignments among four AEs with 16 PEs per AE               | 62 |

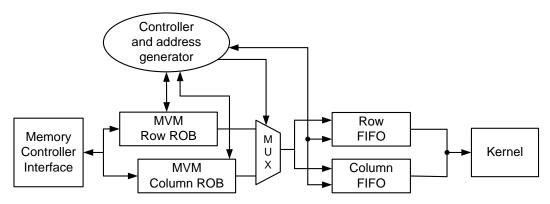

| Figure 5.9 Block diagram of the proposed MVM for each PE                             | 63 |

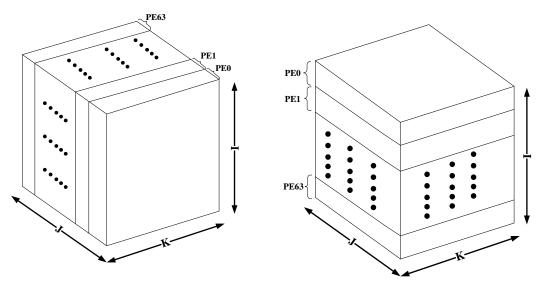

| Figure 6.1 Partitions along the J (left) or I (right) dimensions in 3D stencil space67 |

|----------------------------------------------------------------------------------------|

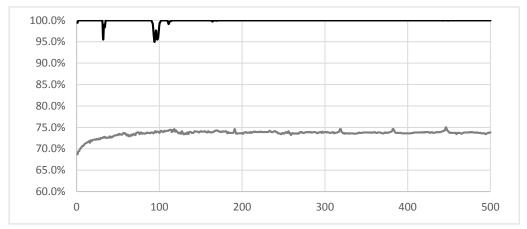

| Figure 6.2 Efficiency vs. the block sizes (K-dimension partition, 6-point stencil)67   |

| Figure 6.3 Efficiency vs. the block sizes (J-dimension partition, 6-point stencil)68   |

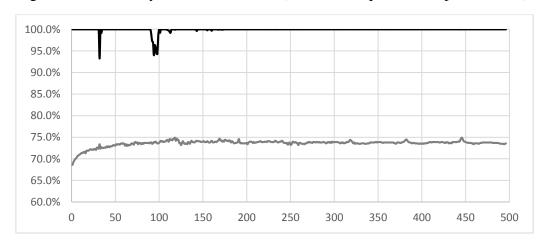

| Figure 6.4 Efficiency vs. the block sizes (I-dimension partition, 6-point stencil)68   |

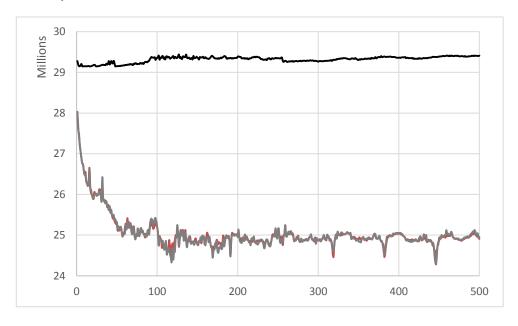

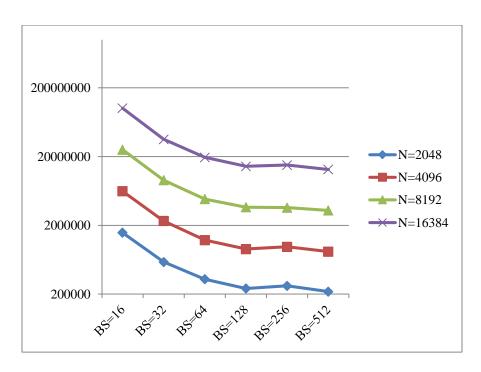

| Figure 6.5 Runtime vs. the block sizes in 3D 6-point stencil                           |

| Figure 6.6 Efficiency vs. the block sizes (K-dimension partition, 27-point stencil)70  |

| Figure 6.7 Efficiency vs. the block sizes (J-dimension partition, 27-point stencil)71  |

| Figure 6.8 Efficiency vs. the block sizes (I-dimension partition, 27-point stencil)71  |

| Figure 6.9 Runtime vs. the block sizes in 3D 27-point stencil72                        |

| Figure 6.10 Block partitions along the J and I dimensions in 3D stencil space74        |

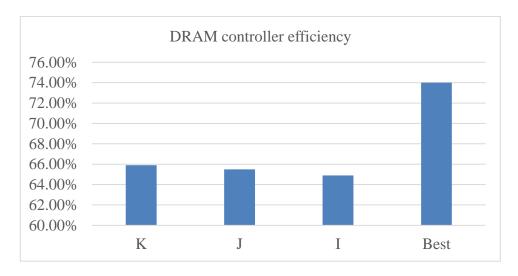

| Figure 6.11 Comparison of 6-point 3D DRAM controller efficiency results78              |

| Figure 6.12 Row-major and column-major stride access orderings for each PE81           |

| Figure 6.13 Scaled runtime vs. matrix and block sizes (No data reuse)84                |

#### CHAPTER 1

#### Introduction

High-performance reconfigurable computing (HPRC) is a computer architecture that combines the potential performance of reconfigurable computing accelerators like FPGAs with the flexibility of conventional general-purpose microprocessors. HPRC is suitable for numerous applications that spend substantial time on a few software kernel loops. Executing these kernels on HPRC systems reduces the execution time as compared to software implementations using general-purpose processors.

In HPRC systems, kernels are implemented with hardware description languages such as Verilog and System Verilog. Some HPRC systems also allow the use of high-level synthesis tools [1,2,3,4] to aid the design implementation and verification of kernels. Current high-density FPGAs enable the implementation of a kernel in a modular fashion to improve design productivity.

An FPGA is an integrated circuit designed to be configured by a customer after manufacturing. An FPGA contains programmable logic components and a hierarchy of reconfigurable interconnects that allow the components to be wired together in many different configurations for any arbitrary digital logic circuit. FPGAs often handle the kernel computation faster than general-purpose processors because they can be fully customized, allowing almost all hardware resources to be dedicated to the computation. On

the other hand, CPUs generally utilize hardware resources less efficiently due to its general-purpose fixed microarchitecture.

The major challenge with designing FPGA-based kernels is that a designer must explicitly define the on-chip portions of memory hierarchy and cannot take advantage of the complex and refined structures on microprocessors that are taken for granted. On many HPRC systems, on-chip components do not exist between memory system and FPGAs, so the designer has to specify the memory access mechanism (e.g., generate memory addresses and employ buffering) to hide memory access latency and reuse commonly occurring items to improve performance. The design and optimization of on-chip components are challenges for the designer.

#### 1.1 MEMORY PERFORMANCE

In HPRC systems, the main applications run on the microprocessors while the FPGAs handle kernels that have long execution time. Such kernels typically present parallel computations that can be efficiently implemented on the FPGAs. To support highly parallel processing on the FPGAs, the memory system in an HPRC system offers very high memory bandwidth and capacity. However, high memory bandwidth and capacity do not lead directly to high increase in the memory system performance. For memory-bound kernels, memory system performance is very important because the overall kernel performance depends on memory system performance. Memory system performance is often characterized by memory latency hiding, memory access scheduling and data reuse.

*Memory latency hiding* overlaps kernel computations with memory accesses. A highperformance microprocessor hides the memory latency through out-of-order instruction execution, nonblocking cache and prefetching. In out-of-order instruction execution,

arithmetic instructions that follow the memory access instruction may bypass the pending memory instruction if there is no data dependency between them. Nonblocking cache also effectively reduces the cache miss penalty by overlapping execution with memory access. It allows the data cache to continue to supply cache hits during a cache miss. Another approach is to prefetch data before they are requested by the processor. The prefetched data can be put into the caches or into an external buffer that can be accessed more quickly than the main memory. In FPGA-based designs, support for memory latency hiding must be explicitly defined by the user based on the characteristics of the memory system on an HPRC platform.

The HPRC memory system generally utilizes a DRAM-based memory system. DRAM is organized in a way in which its effective bandwidth depends on the order in which accesses are made. Some CPUs perform *memory access scheduling* to dynamically schedule memory loads and stores to improve memory performance, but they are limited by the size of the memory load/store queue and/or prefetching accuracy. Other CPUs access the memory in the order statically scheduled by the compiler. An FPGA design of a kernel with a regular access pattern and a priori knowledge of all memory accesses presents a huge potential for scheduling memory accesses insofar as on-chip memory capacity permits. However, the user has to explicitly define memory access orderings based on DRAM architecture and memory access patterns of a kernel to achieve high memory bandwidth.

Data reuse is another memory performance optimization that improves memory performance. It takes advantage of temporal locality of memory accesses to avoid unnecessary off-chip memory accesses. CPUs reuse data in the caches by exploiting

temporal locality of memory accesses. However, conflict misses in a cache still cause some unnecessary memory accesses. In an FPGA design, whenever there is regular access pattern, unnecessary off-chip memory accesses can be completely avoided insofar as the on-chip memory capacity permits. The support for data reuse must be integrated into the design as well.

#### 1.2 OVERVIEW OF DISSERTATION

The Convey HC-1 is a modern HPRC system combining FPGAs with microprocessors. The goal of this dissertation is to develop methodologies that employ memory latency hiding, memory access scheduling and data reuse for two types of memory-bound kernels, matrix vector multiply (MVM) and 3D stencil, on the Convey HC-1 system.

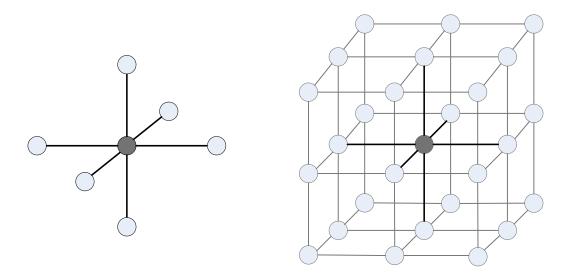

We choose MVM and 3D stencil because both kernels are memory-bound. If the kernel is compute-bound, then its performance is not constrained by the memory performance. We select 6-point and 27-point 3D stencils as examples of simple and complex access patterns, respectively. The larger the number of stencil points, the more memory performance optimizations can be applied, but the fewer FPGA resources available for the implementation.

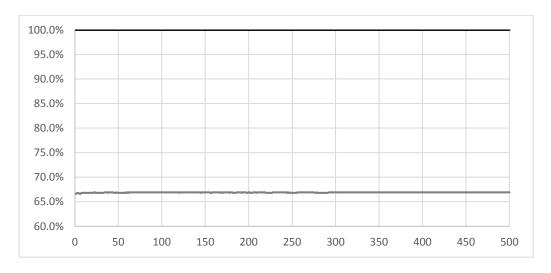

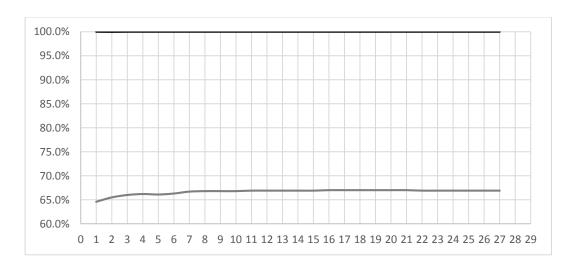

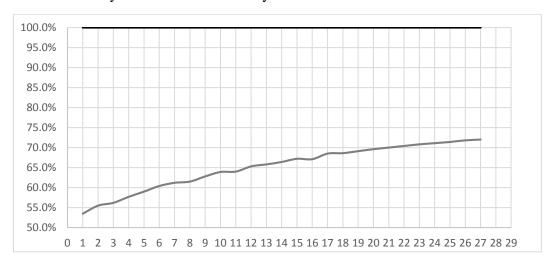

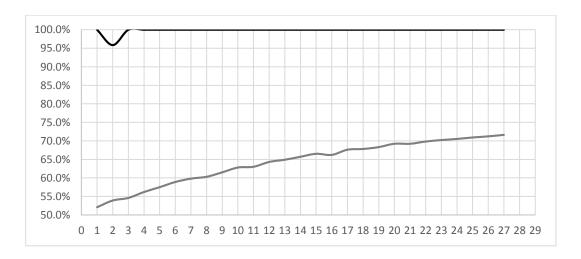

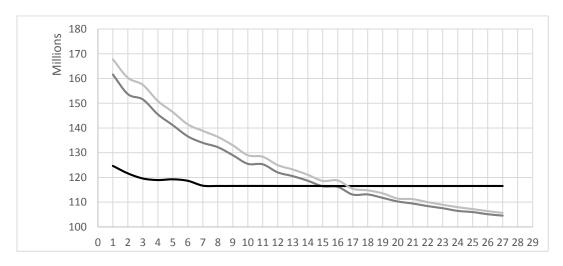

Our approach is to develop an optimized memory controller interface that integrates memory latency hiding, memory access scheduling and data reuse to achieve high overall performance. The goal of memory latency hiding is to maximize *interface efficiency*, the percentage of interface execution time in which memory controller interface performs a memory access. We achieve almost 100% interface efficiency for memory latency hiding.

For memory access scheduling, the goal is to maximize *DRAM controller efficiency*, the percentage of memory access time in which memory accesses are not stalled due to the

conflicts. We improve DRAM controller efficiency from 39% to 88% for MVM without data reuse, and from 42% to 89% for MVM with data reuse, and from 68.7% to 74% for 6-point 3D stencil, and from 52% to 72% for 27-point 3D stencil.

With a limited size of on-chip buffers, the goal of data reuse is to minimize the total number of memory requests required to achieve high *data reuse rate*. Data reuse rate is the ratio of the number of reused memory requests to the total number of memory requests without data reuse. We are able to achieve the reuse rate of about 0.5 for MVM and the reuse rate of 0.6 and 0.9 for 6-point and 27-point 3D stencil respectively.

When combining all three optimizations in the memory controller interface, the goal is to improve (i.e., decrease) the execution time, so the overall performance of the memory controller interface is measured with speedup. Compared to the baseline memory interface designs, we are able to achieve averaged speedup of 1.6 for MVM, 2.2 for 6-point 3D stencil and 9.5 for 27-point 3D stencil, with data reuse contributing the most to the improvement of speedup. The experimental results show that our dissertation can provide design and optimization references to the end-user who needs to parallelize a specific application by implementing it on a multi-FPGA platform.

The rest of the dissertation is organized as follows. Chapter 2 describes the multi-FPGA Convey HC-1 platform. Then it describes the techniques of memory latency hiding, memory access ordering and data reuse in the memory interface. Chapter 3 discusses related work from the perspectives of the target platform, memory latency hiding, memory access scheduling and data reuse. Chapter 4 describes the preliminary results of our work on the Convey HC-1. Chapter 5 presents detailed memory interface designs of the kernels

on the Convey HC-1. Chapter 6 shows the experimental results of memory interface designs on the Convey HC-1. Chapter 7 concludes the dissertation.

#### **CHAPTER 2**

#### **BACKGROUND**

#### 2.1 HIGH-PERFORMANCE RECONFIGURABLE COMPUTING (HPRC)

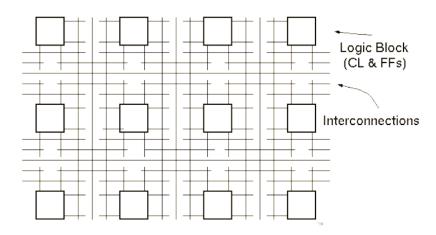

Field Programmable Gate Arrays (FPGAs) are semiconductor devices that are built on a matrix of configurable logic blocks (CLBs) connected via programmable interconnections. Each CLB is basically composed of combinational logic (CL) and flip-flops (FFs). Figure 2.1 shows a simplified version of an FPGA internal architecture. As opposed to Application Specific Integrated Circuits (ASICs), where the devices are built specifically for an

Figure 2.1 Simplified version of FPGA internal architecture

application, FPGAs can be programmed to the desired application or functionality requirements. Due to FPGAs' programmable characteristics, they are widely used in fields of vehicles, consumer electronics, high-performance computing, video and image

processing. Two large companies, Altera and Xilinx, provide the broadest lineup of FPGAs with advanced features, low power, and high performance, for any FPGA designs [5,6].

What are the benefits of having FPGAs in an HPRC system? The potential speed benefits of using FPGAs are huge when taking advantage of massive parallelism in FPGAs. FPGAs also provide designers full control at the lowest hardware level, allowing fine-grained, manual optimizations for each application. In addition, FPGAs are low-power devices compared to traditional microprocessors. The power consumption of a typical design in FPGAs is very low. Finally, FPGAs are flexible in the reconfiguration of hardware accelerators for multiple applications.

The concept of reconfigurable computing has existed since the 1960s, when the concept of a computer made of a standard processor and an array of reconfigurable hardware was proposed [7,8,9]. The aim of the reconfigurable computing is to combine the flexibility of software with the speed and configurability of the hardware, with a main processor controlling the behavior of the hardware. Unfortunately the concept was not realizable until the advancements in silicon process technology allowed complex designs to be implemented on large and very large-scale integrated circuits.

Early HPRC systems were designed around one node of microprocessors and another of FPGAs. The two nodes were connected directly without a scalable interconnection. The modern architecture of scalable parallel systems is grouped into two classes based on the types of the nodes and how they are connected. In uniform node nonuniform systems, each node has either FPGAs or microprocessors and the nodes are connected via an interconnection network to globally shared memory. In nonuniform node uniform systems, there is only one type of node and each node contains FPGAs and microprocessors. FPGAs

are connected directly to the microprocessors in the node. The nodes are connected the same way as in uniform node nonuniform systems.

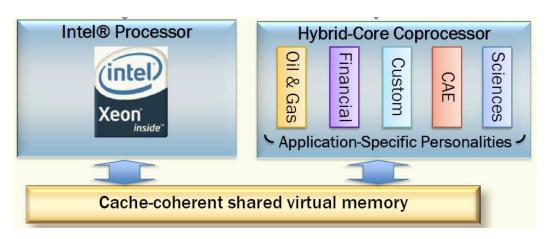

Figure 2.2 Convey's hybrid-core computer [10]

The Convey HC-1 platform, the first of a series of Convey's high-performance reconfigurable computing products, was unveiled in 2009. The reconfigurable computing system combines commodity Intel processors with a reconfigurable coprocessor based on FPGA technology. Figure 2.2 illustrates Convey's hybrid-core computer. The coprocessor can be dynamically reloaded with custom instructions that are optimized for different workloads. The instructions are a combination of x86 set of instructions and reloadable set of instructions. The reloadable set of instructions is called a personality. The platforms also feature globally shared memory that supports a standard load/store programming model. In the globally shared memory model, both the processor and the coprocessor have copies of the global memory space through a cache-coherent shared virtual memory.

#### 2.2 DYNAMIC RANDOM ACCESS MEMORY

The memory system in an HPRC system provides very high memory bandwidth and capacity to support the highly parallel, high bandwidth processing of the coprocessors. In

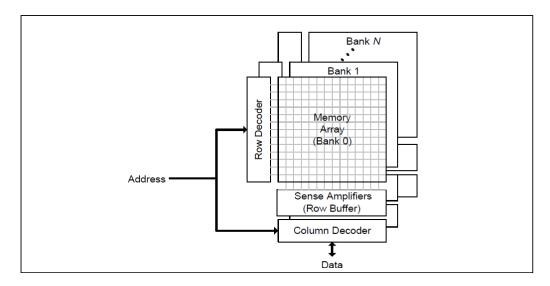

Figure 2.3 Modern DRAM organization

such memory system, multiple DRAM devices are interconnected together to form a memory system managed by one or more memory controllers. The functionality of a memory controller is the read or write requests to a given address in DRAM in accordance with the DRAM access timing requirements. DRAM is logically a 3D memory with the dimensions of bank, row and column. Figure 2.3 shows the logical organization of a modern DRAM. Each bank operates independently of the other banks and contains an array of memory cells that are accessed an entire row at a time. Modern DRAM devices contain multiple banks so that multiple, independent accesses to different DRAM arrays can happen in parallel. When a row of the memory array is accessed (row access) through the row decoder, the entire row (a.k.a. a DRAM page) is latched into the sense amplifiers (row buffer). The row buffer reduces the latency of subsequent accesses to that row. The time it takes to move data from the memory array to the row buffer is known as the Row Column Delay (RCD). When a row is held in the buffer, any number of reads or writes (column access) may be performed through the column decoder. Read data, for example, are moved

from the sense amplifiers of a given bank to the memory controller. The time it takes to move the data from the sense amplifier to the memory controller after initiation of column access is known as the Column Access Strobe (CAS) latency. The CAS latency measures the time to transfer the first word of memory. After the reads or writes are complete, the row must be written back to the memory array through bank precharge to prepare the bank for a subsequent row access. A detailed introduction to the DRAM organizations, operations, timing, and the basic nomenclature can be found in [11].

Modern HPRC systems are becoming increasingly limited by DRAM based memory system performance. To improve memory performance, modern DRAM provides several independent memory banks, buffers the most recently accessed row of each bank and allows pipelined and burst memory accesses. Though these device-level optimizations increase the memory performance, they make memory performance dependent on the specific memory interface in the HPRC system. The functionality of memory interface is to efficiently manage the memory accesses to the memory system to achieve high system performance.

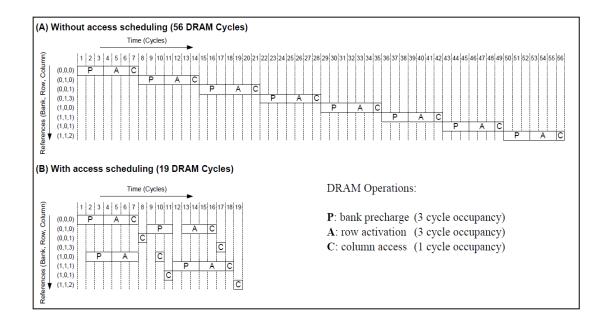

Memory access scheduling or ordering is an effective way to improve the memory performance. It is a mechanism of ordering the memory accesses to complete the set of pending memory references. Figure 2.4 shows the sequence of eight memory operations on DRAM. Each memory reference is represented by the address (bank, row and column) and we assume 3 cycles, 3 cycles and 1 cycle are required for bank precharge, row access and column access respectively. If the eight memory operations are performed in order, 56 cycles are needed to finish the eight references. If the memory references are reordered, they take only 19 cycles.

Figure 2.4 Memory access scheduling of eight memory operations.

The figure is from [12]

Another way to improve the overall performance of an HPRC system is the use of onchip buffers for hiding the latency of memory access. As compared to the general-purpose processors that have hardware-managed caches to hold frequently accessed data, the onchip buffers in the FPGAs store frequently accessed data. The overall performance increases significantly as the latency of accessing on-chip data is much faster than off-chip

Figure 2.5 Convey HC-1 memory architecture

DRAM access. In addition, the on-chip buffers presents opportunities for data reuse, i.e., the access of data in the buffers more than once during application execution. By storing and accessing the reusable data in the on-chip buffers, the memory bandwidth contention is decreased, which in turn reduces memory access latency and improves the overall performance.

#### 2.3 CONVEY HC-1 MEMORY SYSTEM

The Convey HC-1 is a high-performance reconfigurable computer containing an FPGA-based coprocessor attached to a host motherboard through a socket-based front-side bus interface. Unlike socket-based coprocessors from Nallatech [13], DRC [14], and XtremeData [15], which are confined to a footprint matching the size of the socket, Convey uses a mezzanine connector to bring the front side bus (FSB) interface to a large coprocessor board roughly the size of an ATX motherboard. This allows the coprocessor memory to be coherent with the host CPU's memory while providing sufficient real estate for the coprocessor board to be capable of hosting multiple large user FPGAs and a large and sophisticated memory system.

As shown in Figure 2.5, the coprocessor board contains four user-programmable Virtex-5 LX 330 FPGAs that Convey refers to as "application engines (AEs)". The coprocessor board also contains eight discrete memory controllers, each of which is implemented on its own Virtex-5 LX 110 FPGA. The memory space of the coprocessor board is physically partitioned into eight equal-size segments, and each segment is only accessible from one of the eight memory controllers. Specifically, each memory controller can access 64 contiguous bytes within each block of 512 contiguous bytes. Each AE is

connected to all eight memory controllers through a crossbar switch that is instanced on each memory controller.

The interface between each AE and each memory controller allows up to two independent 64-bit memory transactions (read or write) per cycle on a 150 MHz clock, giving a peak theoretical bandwidth of 2.4 GB/s per memory controller, or 19.2 GB/s per AE, or 76.8 GB/s aggregate bandwidth for the coprocessor board [16]. In practice, each AE "sees" a memory interface consisting of 16 64-bit wide channels.

Memory addresses are virtual and mapped to 4 MB pages. Each memory controller contains a translation lookaside buffer (TLB) to cache the page table. Within each 4 MB page, the memory address is divided into the following physical fields as listed in Table 2.1. Each of the eight memory controllers are connected to two DIMMs, which are selected by bit 9. Both DIMMs contain eight DRAMs (i.e., eight 8-bit busses) and each DRAM has eight banks that can be accessed independently by the memory controller. The division

Table 2.1 Divisions of memory address fields

| Bit Field | Field Size | Field Name        |

|-----------|------------|-------------------|

| 21:20     | 2          | DRAM row          |

| 19:13     | 7          | DRAM column       |

| 12:10     | 3          | DRAM bank         |

| 9         | 1          | DIMMs select      |

| 8:6       | 3          | Memory controller |

| 5:3       | 3          | DRAM bus          |

| 2:0       | 3          | Byte alignment    |

(mapping) of memory address fields implies that the requests are interleaved across the memory controllers as well as across the banks within the DIMMs attached to each memory controller. This ensures that sequential accesses will be spread across all 16 DIMMs, maximizing concurrency and bandwidth.

Each of the memory controllers also attempts to maximize bandwidth by scheduling incoming memory requests to each of the banks on its DIMMs, routing requests to non-busy banks and grouping reads and writes into bursts to minimize bus turns (state change between read and write). As a result, memory accesses are performed in a different order in which they were requested by the user. Since Convey will not reveal implementation details nor provide a cycle-accurate model of the memory controller, we performed a bandwidth test that accesses all the 65536 64-bit words accessible from a single memory controller within a single page. The effective bandwidth given by the Convey memory controller with various access patterns will be characterized in Chapter 4.

#### 2.4 MEMORY ACCESS ORDERING ON THE CONVEY HC-1

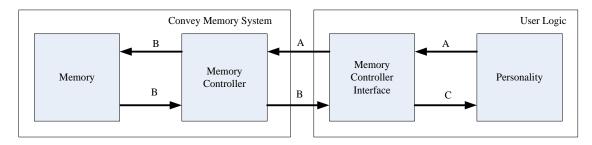

Apart from the memory access scheduling in the memory controller, the memory controller interface introduces memory access orderings from the perspective of custom personality. In other words, a custom personality can request the memory through the memory control interface in different access orders. Figure 2.6 gives an overview of the memory access orderings A, B, and C that occur on the Convey HC-1 platform. Different memory access orderings may be performed among the personality, the memory controller interface, the memory controller and the memory. While the memory access ordering at B depends on Convey's proprietary memory controller, the ordering at A depends on the access orders of the custom personality. For example, a personality that implements a loop kernel of

vector addition, may request an element of each array for the current loop iteration before proceed to request the elements of the next iteration. Alternatively, the personality may request two elements of one array for the two loop iterations before proceed to request two

Figure 2.6 Memory access orderings on Convey HC-1

elements of another array. The ordering at C may be the same as the ordering at A when the receiving data return to the personality in the same order as the data requests from the personality. The ordering at C may also be different from the ordering at A when the data from the memory controller interface can be reused by the personality. In this case, the personality only needs to request the data once and the return data can be reused by the personality. In the dissertation, we explore the memory access ordering at A for the application-specific personalities to improve memory performance.

#### 2.5 MEMORY LATENCY HIDING ON THE CONVEY HC-1

On the Convey HC-1 platform, the memory access latency is around 256 clock cycles. To hide the long memory latency, the memory controller interface needs to support pending memory requests to efficiently utilize the memory bandwidth. When requested data return from the memory, they are stored in the on-chip buffers from which the kernel read the input data for computation. To parallelize the kernel computation with the memory requests, the memory interface uses more than one buffer (multiple buffering) to hide the memory

latency. Multiple buffering delivers a stream of inputs from the DRAM-based memory system to the kernel while minimizing the number and length of stream interruptions.

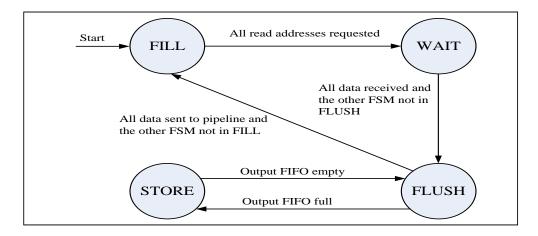

#### 2.5.1 DOUBLE BUFFERING

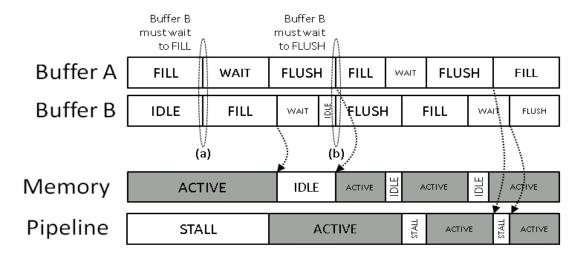

The first attempt at memory interface design used a double-buffering (ping-pong) approach, where data returned from the memory controller fill one buffer while the contents of the other buffer are flushed into the pipelined kernel. To simplify the control of double-buffering, each of the two buffers has its FSM-based controller, shown in Figure 2.7. Each buffer proceeds through a sequence FILL, WAIT, and FLUSH with occasional transitions between FLUSH and STORE. In FILL, the buffer requests a sequence of load addresses from the memory channel. After all the addresses have been requested, the controller enters the WAIT state, where it waits for all the requested data to be delivered from memory. After all input values are delivered to the input buffer, the buffer enters the FLUSH state in which all the stored input values are sent into the pipelined kernel (assuming the other buffer has completed its own FLUSH procedure). Since both buffers share a single memory channel, only one buffer can be in the FILL state at a time. Likewise, since both buffers

Figure 2.7 Double-buffering control FSM

are sharing a single kernel pipeline, only one buffer can be in the FLUSH state at one time. This yields a combined behavior as shown in Figure 2.8. The top two horizontal lines represent the state transitions of both buffers. The bottom two horizontal lines represent when memory requests are being made (top) and when the kernel pipeline is enabled (bottom). As shown, buffer A is the first to enter the FILL state, while buffer B must wait. This is shown at point (a). The time required in the FILL state depends on the number of stall requests issued by the MC. After buffer A issues all of its memory read requests it transitions to the WAIT state to wait for the input data to be delivered from MC. The amount of time required in the WAIT state depends on the average memory latency. After all data are received, buffer A transitions to the FLUSH state to send its buffer contents into the pipeline. The number of cycles required in the FLUSH state is fixed. However, as shown at point (b), buffer B must wait until buffer A completes its FLUSH before it can also transition to FLUSH. During the time that elapses after buffer B completes its FILL and before buffer A completes its FLUSH, the memory channel is idle. Likewise, during

Figure 2.8 Double buffer behaviors and memory interface and pipeline utilization

the time that elapses between buffer A's subsequent FLUSH and buffer B's next FLUSH, the pipeline is idle.

The analysis of Figure 2.8 shows that the memory interface is idle when both buffer are in the WAIT state or one buffer is in the WAIT state while the other in the FLUSH state. In addition, the kernel pipeline is stalled when one buffer is in the FILL state and the other in the WAIT or IDLE state. These overlapping intervals introduce the inefficiency of the memory interface design with double buffering. Thus, the memory latency is not entirely hidden due to the contentions of the buffers for memory accesses and kernel pipeline.

#### 2.5.2 CIRCULAR BUFFERING

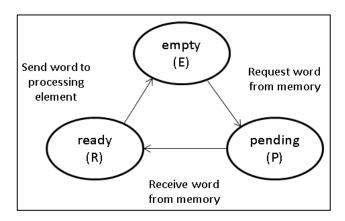

In recent releases on Convey's Personality Design Kit, they included an optional memory reorder buffer that forms an interface between the user logic and the memory controller. The reorder buffer sends the requested words back to the user logic in the order they were requested from the user logic. As shown in Figure 2.9, when a request is received from the user logic, the reorder buffer's state transitions from *empty* to *pending*. When the

Figure 2.9 State transitions of the reorder buffer

Table 2.2 Memory operations of read reorder buffer

| Cycles | Address<br>generator                           | Reorder buffer                                                                            | Memory<br>controller<br>interface                                        | Buffer state                                                    |

|--------|------------------------------------------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-----------------------------------------------------------------|

| 0-3    | Load addresses<br>of A[0], B[0],<br>C[0], D[0] | Request A[0],<br>B[0], C[0], D[0]<br>from memory                                          | Nothing                                                                  | read ptr write ptr  d B C D X X X X X X X X X X X X X X X X X X |

| 4-7    | Load addresses<br>of A[1], B[1],<br>C[1], D[1] | Request A[1],<br>B[1], C[1], D[1]<br>from memory                                          | Deliver values<br>of A[0], C[0],<br>D[0] from<br>memory to the<br>buffer | read ptr write ptr  addr ABCDABCDXXXXXX  state RPRRPPPPEEEEEEEE |

| 8-11   | Load addresses<br>of A[2], B[2],<br>C[2], D[2] | Return A[0] to<br>user  Request A[2], B[2], C[2], D[2] from memory                        | Deliver values<br>of B[0], C[1],<br>D[1] from<br>memory to<br>buffer     | read ptr write ptr  ↓  addr                                     |

| 12-15  | Load addresses<br>of A[3], B[3],<br>C[3], D[3] | Return B[0],<br>C[0], D[0] to<br>user<br>Request A[3],<br>B[3], C[3], D[3]<br>from memory | Deliver values<br>of A[1], B[1],<br>B[2] from<br>memory to<br>buffer     | write ptr read ptr  dddr                                        |

memory controller returns the requested word, the word is stored in the reorder buffer and marked as *ready*. When the read pointer points to a buffered word that is marked as ready, its value is sent back to the user logic.

Table 2.2 illustrates the operations of the reorder buffer. Assume the user logic implements a loop that computes an expression requiring one element from each of four arrays, A, B, C, and D. The kernel pipeline expects one entry from each array to be delivered in sequence, i.e., A[0], B[0], C[0], D[0], A[1], B[1], etc. The reorder buffer is based on a queue implemented as a circular buffer. As opposed to the double buffering where there are front and back buffers, the circular buffer has a single buffer that functions

as both front and back buffers. When the user logic performs a load request, the state of the request is enqueued in the FIFO using a write pointer, it is requested from the memory controller, and its status is monitored.

Compared to the double buffering technique in which the memory interface could be idle without memory requests, our FPGA tests based on the kernel benchmarks show that the reorder buffer doesn't introduce any idle or stall cycles.

#### 2.6 DATA REUSE ON THE CONVEY HC-1

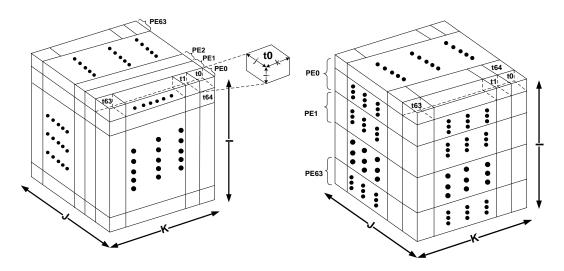

Data transfers between the DRAM-based memory system and the processing elements are often the performance bottleneck when using reconfigurable logics in FPGAs as a hardware accelerator. As a result, the use of on-chip buffers to store repeatedly accessed data is an effective way to reuse the data and increase the memory access bandwidth. The on-chip buffers are typically implemented using FPGA's embedded RAM blocks. Given the architecture of the Convey HC-1 memory system in which each AE has 16 memory channels with each channel composed of request and response ports, the kernel computation is divided among 16 PEs per AE for maximum parallel execution and memory access bandwidth. Each PE accesses its on-chip buffers for reused data.

While each PE uses on-chip buffers for fast access to the reused data, the amount of reused data, however, is much larger than on-chip memory capacity. On-chip buffers have large bandwidth but limited size due to the number of available embedded RAM blocks on the target FPGAs. This means that some redundant memory accesses are still required as the on-chip memories cannot hold all reused data. So the buffers are updated at runtime based on the memory access patterns of the kernels. In section 2.9, we will define data reuse rate to measure the efficiency of data reuse.

#### 2.7 BUFFERING FOR MEMORY LATENCY HIDING AND DATA REUSE

From the descriptions in sections 2.5 and 2.6, the on-chip buffers assume the roles of memory latency hiding and data reuse. Convey's circular buffering is better than double buffering in memory latency hiding because it doesn't introduce idle or stall cycles. In circular buffering, the reorder buffer sends the requested words back to the user logic in the order they were requested from the user logic. The problem with the reorder buffer is that once the requested words return to the user logic, they are not available in the reorder buffers for reuse. On the other hand, to reuse the requested words they must be kept (until they have to be updated due to the limited size of buffers) in buffers after they have been read. To achieve both memory latency hiding and efficient data reuse, the memory interface has two kinds of buffering for each PE: the reorder buffer requests memory and returns the requested words in order while custom circular buffer stores and accesses the requested data in a way suitable for reuse. This approach realizes the advantage of each buffer so that the reorder buffer returns the requested data without interface stall and the custom buffer is focused on maximizing data reuses.

#### 2.8 PERFORMANCE MEASUREMENT

Chapter 1 briefly mentions overall performance metric and memory performance metrics for memory latency hiding, memory access scheduling and data reuse. For memory-bound kernels, the user logic attempts to access memory during every clock cycle of operation. Any cycle where the logic does not access memory is either due to inefficiency in the memory controller interface designs or due to a stall request from Convey's memory

controller. To evaluate the efficiency of memory controller interface design, we compute interface efficiency as:

Interface efficiency =  $(rc + wc) / (execution \ time - sc)$ ,

where rc is the number of memory reads (loads) and wc the number of writes (stores) for each PE. Execution time is the time lapse from the time when all PEs in an AE start the kernel computation to the time when all PEs finish the kernel computation. Since not all PEs finish their kernel computation at the same time, the execution time is the worst runtime of all PEs. Similarly, sc is the maximum number of stall cycles among all PEs in an AE.

DRAM controller efficiency differs from interface efficiency in that it does not consider any inefficiency in the kernel design. To measure the performance of memory access scheduling, DRAM controller efficiency is computed as:

$DRAM\ controller\ efficiency = (rc + wc)/(rc + wc + sc),$

where rc is the number of memory reads (loads) and wc the number of writes (stores) that access a DRAM controller via its even and odd ports. As the crossbars distribute the memory requests of four AEs across eight DRAM controllers, we assume the number of memory accesses (rc + wc) to a DRAM controller is the number of memory accesses of all PEs of four AEs that are connected to the DRAM controller. sc is the sum of read and write stall cycles requested by the DRAM controller at its even and odd ports in a PE.

Assuming that memory requests are performed every execution cycle, the effective memory bandwidth of each memory channel can be computed as:

$BW = 1.2 \text{ GB/s} \times Interface \ efficiency \times DRAM \ controller \ efficiency$

To measure the efficiency of data reuse, the *reuse rate* is computed as the ratio of the number of reused memory requests and the number of memory requests before (without) data reuse:

Reuse rate = (M1 - M2)/M1,

Where M1 - M2, the number of reused memory requests, is the difference of the number of memory requests before and after data reuse.

Since interface efficiency does not take into account any memory stalls, it is expected to be higher than DRAM controller efficiency. Just as the cache performance in a memory hierarchy is evaluated by the memory access time, we evaluate overall performance combining memory latency hiding, memory access scheduling and data reuse by the execution time. When combining all three optimizations in the memory controller interface, the goal is to improve (i.e., decrease) the execution time. We use speedup, the ratio of the execution time of two implementations with different optimizations, to compare the overall performance of the designs. In the Chapter on experimental results, we will define speedup in the context of specific implementations for each kernel.

#### **CHAPTER 3**

#### RELATED WORK

#### 3.1 THE CONVEY HC-1 SYSTEM

The Convey HC-1 is a modern HPRC system. A few papers on the system were published to study the software/hardware interfaces, the programming methodologies, design and implementation optimizations, and system performance. However, the improvement of memory performance on the Convey HC-1 has not been studied well in the past.

Bakos examined the Convey HC-1 system in terms of system architecture, performance, ease of programming and flexibility [17]. The paper shows that the Convey system achieves better results than a CPU for memory-intensive applications such as Stride3 benchmark and Smith-Waterman algorithm. In [18] the authors analyzed the programming paradigm, the associated programming effort, and presented practical results on the Convey HC-1. Using a 3D 7-point stencil for solving the Laplace equation on grids of different sizes, they compared the peak floating-point performance on the Convey HC-1 and on a 2-way 2.53-GHz Intel Nehalem processor. They showed that the stencil performance on the Convey HC-1 is lower on smaller grids due to the lack of caching.

At the hardware design level, Ruthenberg [19] used the ROCCC compiler with Convey HC-1 support to generate the vector addition personality and evaluated the memory throughput using Convey's crossbar and read order buffer. The results show that

the highest memory throughput is achieved when a read reorder buffer is instantiated alone as opposed to the combination of crossbar and read reorder buffer.

Cong et al. [20] reported their implementations of a memory-bound application on the Convey HC-1 and GPU platforms. Their FPGA design is around 30% faster than the GPU implementation and consumes less than half of the power consumption. However, the memory efficiency is around 30% on both platforms though the design utilizes all the memory access ports on the Convey HC-1.

Recently Nowak et al. [21] presented a highly parallel architecture that exploits the massive parallelism on the Convey HC-1 to accelerate prefiltering in HHblits. They achieved application speedup of 1.79 against the original, unmodified state-of-the-art SSE-based implementation. By considering data reuse, they transformed the memory-bound, SSE-based algorithm to a compute-bound FPGA implementation that has an average throughput of only 69 MB/s. The paper, however, does not mention memory efficiency of the memory system.

# 3.2 MEMORY ACCESS SCHEDULING

Memory access scheduling is an effective way to improve DRAM-based memory efficiency where the memory performance depends on how DRAMs are accessed by the DRAM controllers. Scott et al. [10] introduced the concept of ordering memory references to exploit locality within the 3-D memory structure. They described DRAM architectures and presented the memory controller architecture that supports memory access ordering. They showed that conservative and strong orderings can improve memory bandwidth by 40% and 93% respectively for a set of media benchmarks.

Zhang et al. [22] proposed a fine-grain priority scheduling method, which divides and maps memory accesses into different channels and returns critical data first, to fully utilize the available bandwidth and concurrency provided by DDR SDRAM and Direct Rambus DRAM systems in simultaneous multithreading systems. They showed DRAM optimizations make a larger difference than on single-threaded systems for workloads with intensive memory demands.

Fang et al. [23] proposed a core-aware memory access scheduling that classifies outstanding requests from the same processor core and issue them together. The idea is that the requests from the same core more likely exhibit data locality than the requests from different cores. A threshold of the maximum number memory requests is also set to prevent starvation of memory requests from other cores. Their simulation results on Solaris OS show that OS task scheduling schemes reduce the performance improvement of the benchmarks running with multiple threads.

Mutlu et al. [24] proposed a Stall-Time Fair Memory scheduler to provide quality of service to different threads using the DRAM memory system. Their scheduler achieves stall-time fairness by prioritizing requests from threads with very high memory slowdown. The memory slowdown is memory stall time of a thread running alongside other threads versus the stall time of the thread running alone. The scheduler is an extension to the first-come-first-serve scheduler with the additions of slowdown estimation and priority policy. The experimental results running on an 8-core chip multiprocessor show an average throughput improvement of 7.6%.

Yuan et al. [25] proposed a complexity-effective memory access scheduling for GPU architectures. They employed an interconnection network arbitration scheme that preserves

the row access locality of each memory request streams to achieve DRAM efficiency. There is up to 91% performance improvement on the architecture with 8 memory channels, each controlled by its own DRAM controller and 1,792 in-flight memory requests. In [26], the authors proposed a CUDA-based API that allows programmer to improve the efficiency of memory accesses on the GPU platform. They added memory layout remapping and index transformation to NVIDIA's CUDA API and achieved about 3x speedup on GPU kernels and 20% overall performance improvement.

#### 3.3 MEMORY LATENCY HIDING

Various software and hardware techniques of memory latency hiding have been proposed to improve the memory performance on the VLIW, HPRC and GPU architectures. The Decoupled Access/Execute architecture [27] in the early research decouples memory access and instruction execution. The access processor performs all memory access and address calculation; the execute processor does the computation. The communication between two asynchronously running processors is via the queues. The decoupled architecture hides memory latency by overlapping computation with memory transfer. Decoupled architectures are not very useful for general purpose computing as they don't handle controls and branches well, but they play an important role in scheduling in VLIW architecture. On HPRC platforms, decoupled architectures may be drawn as a reference to exploit parallelism between memory access and kernel computation to improve performance.

Software techniques were also proposed to hide the memory latency. Chen described a memory latency hiding algorithm that combines the loop pipelining with data prefetching [28]. The algorithm divides the iteration space into regular partitions, and then produces

two parts of a schedule for ALU and memory operation in a nest loop. They studied the optimal partition shape and size for a well-balanced overall schedule. Xue et al. [29] proposed a software prefetching technique that can completely hide memory latencies for applications with multi-dimensional loops on architectures like CELL processor. They presented an algorithm, iterational retiming with partition, to achieve complete memory latency hiding for multi-core architectures.

For reconfigurable computers, Lange et al. [30] described a parameterized memory system suitable as target for high-level language to hardware compiler. The system combines support for control speculation, distributed memories, and clustered coherence mechanisms. Their experimental results using four benchmarks show that control-intensive codes gains much more from speculation than other types of codes. The speculation allows the hiding of memory latencies, but is limited to 10% improvement for some benchmarks that search for random key values.

Thielmann et al. [31] presented a compiler framework capable of generating application-specific microarchitectures supporting load values speculation on reconfigurable computers. They examined the re-execution control mechanisms, the associated speculation queues that resupply the appropriate data items, and the actual speculation predicators. All the techniques have been implemented in their hardware/software co-compiler. The experimental results show a 2.48x speedup over nonspeculative implementations.

### 3.4 DATA REUSE

Data reuse has been widely studied for bandwidth optimization during the past. In [32], the authors introduced a formal model for data reuse analysis by applying algebraic techniques

specific to the data-flow analysis used in modern compilers. The analysis allows partitioning the index space of arrays in data-dominated application such that the heavily accessed array parts are used as redundant data in scratch-pad memories to reduce the dynamic energy consumption due to memory accesses.

In [33], the authors presented a multiprocessor data reuse analysis technique to enable the designer to explore solutions that meet power and area constraints while maintaining the necessary performance level. They described a shared buffer that can be accessed by multiple processors to reduce the number of accesses to main memory.

In [34] the authors introduced data block reuse to maximize the reuse of a data block before access the next data block. Their approach was based on dividing large data structure into logical blocks and clustering computations that access the same data block using a scheduler. They implemented a software-managed on-chip memory and gave no experimental results.

Wang et al. [35] summarized the research works in [36,37,38,39,40,41] and concluded that the reuse buffer is designed for sequential execution model and thus causes memory access conflict and low throughput in pipelined loops. They also studied the work in [42,43,44,45,46,47] and pointed out that these memory mapping and partitions approach fail to work when data reuse is performed in a non-affined, circular manner to save buffer size. Based on the previous work, they presented an integrated automatic approach for combining memory partitioning and merging with data reuse and pipelining to generate a memory optimization flow for FPGA behavioral synthesis. However, memory latency hiding is not part of their memory optimization flow.

### 3.5 3D STENCIL

Of all kernels selected for experiment in the dissertation, the 3D stencil is the most complex kernel. In [48] Brown evaluates efficient implementations of 2D finite-difference modeling. For evaluation Brown compared FPGA, quad-core and Cell machines. The best speedup was achieved by the FPGA implementation, but the work focused on 2D stencil computations.

The hardware implementations and optimizations for 2D and 3D stencils in the FDTD simulation and seismic imaging problems were proposed by He et al. [49,50,51]. The authors proposed to exploit data reuse of some grid values by sending grid values from the input cache to a set of cascaded FIFOs. The number of FIFOs depends on kernel's order of accuracy with respect to time and space. In 3D stencil each FIFO buffers 2D pages and each page generally contains hundreds to thousands of grid points along each spatial axis. So the onboard memory bandwidth has to be sacrificed to meet the buffering requirements. The authors didn't explore the memory access ordering to improve the performance.

Most work on stencil implementations has been done in the context of processor architectures. General microprocessor based solutions for solving scientific problems in three dimensions are cache-inefficient due to the high miss-rates for the large 3D arrays. In [52] the authors showed tiling is not needed for 2D stencil codes and developed techniques to apply tiling in 3D stencil codes by selection of non-conflicting tiles and/or padding array dimensions to eliminate cache access conflicts. Leopold [53] provides an analytical treatment to the problem to show the effects of tiling in Jacobi and Gauss-Seidel kernels on a 3D array. They proved a lower bound to the capacity miss of a cache of size C for an array of size N<sup>3</sup>. They showed that rectangular tiles outperform square tiles for

row-major storage order. Kamil et al. [54] investigated the impacts of trends in memory subsystems on cache optimizations for stencil computations. They considered the blocking strategies on prefetch-enabled microprocessors. They found that cache blocking is effective only for very large problem sizes and the software and hardware prefetching improved performance of long stride-1 accesses.

The research in [55] explored double-precision 3D stencil computations on the multicores by developing numerous optimization strategies and an auto-tuning environment. To hide memory latency, they employed hardware prefetching, software prefetching, DMA, and multithreading. They explored the technique of circular buffer for both read and write planes to minimize memory traffic. The advantage of the circular queue is the potential avoidance of cache's conflict misses.

# CHAPTER 4

## PRELIMINARY RESULTS

This chapter presents preliminary results of DRAM scheduling, memory latency hiding using double buffer, data reuse analysis and kernel bandwidth requirement. We performed all memory performance tests on the Convey HC-1 platform. The experiment in DRAM scheduling shows how the performance of Convey's DRAM controller depends on the memory access orders. The memory latency hiding test shows double buffering is not perfect due to the interface stall rate. We also calculate theoretical data reuse rate to show the benefit of data reuse for the kernels. In addition, we characterize the bandwidth requirement of 3D stencil kernel to show that 3D stencil is a memory-bound kernel. These results provide a basis for better understanding memory interface designs and implementations of memory-bound kernel.

### 4.1 IMPACT OF DRAM SCHEDULING

As described in Chapter 2, the Convey HC-1's proprietary DRAM controllers attempt to maximize memory bandwidth by dynamically scheduling incoming memory requests, which results in memory accesses performed in a different order in which they are requested by the user. In order to investigate the effective bandwidth given by the memory controller with various access patterns, we designed a memory test kernel that accesses all the 65536 64-bit words accessible from a single memory controller within a single page.

There are 120 (5!) possible access orders that define the relative frequency of when the address in each of the five fields changes. For example, for the following ordering: DRAM bus, DRAM bank, DIMMs select, DRAM column, DRAM row, an access pattern would access all eight words within a bus before changing the bank address, all eight banks before changing the DIMM address, both DIMMs before changing the column address, and all 128 columns before changing the row address.

Table 4.1 DRAM controller efficiency test with 120 access orders

| Access Orders         | Efficiency | Access Orders         | Efficiency |

|-----------------------|------------|-----------------------|------------|

| bank,dimm,bus,col,row | 0.93       | bank,col,bus,row,dimm | 0.19       |

| bank,dimm,bus,row,col | 0.93       | bus,row,dimm,col,bank | 0.19       |

| dimm,bank,bus,row,col | 0.92       | dimm,col,bus,bank,row | 0.19       |

| dimm,bank,bus,col,row | 0.92       | bank,col,dimm,row,bus | 0.18       |

| bus,dimm,bank,row,col | 0.92       | bus,col,row,bank,dimm | 0.17       |

| bus,dimm,bank,col,row | 0.92       | bus,row,col,bank,dimm | 0.17       |

| dimm,bus,bank,col,row | 0.92       | col,dimm,bus,bank,row | 0.16       |

| dimm,bus,bank,row,col | 0.92       | bank,col,row,dimm,bus | 0.15       |

| bus,bank,dimm,col,row | 0.92       | dimm,col,bus,row,bank | 0.15       |

| bus,bank,dimm,row,col | 0.92       | col,dimm,bus,row,bank | 0.15       |

| bus,dimm,row,bank,col | 0.91       | bank,row,col,dimm,bus | 0.15       |

| dimm,bus,row,bank,col | 0.91       | col,bus,dimm,row,bank | 0.15       |

| bus,bank,row,dimm,col | 0.90       | col,bus,dimm,bank,row | 0.14       |

| bank,dimm,row,bus,col | 0.88       | bank,col,row,bus,dimm | 0.13       |

| dimm,bank,row,bus,col | 0.87       | col,bus,bank,dimm,row | 0.13       |

| bank,row,bus,dimm,col | 0.84       | bank,row,col,bus,dimm | 0.12       |

| bus,row,bank,dimm,col | 0.80       | col,bus,bank,row,dimm | 0.12       |

| dimm,row,bank,bus,col | 0.66       | bank,row,dimm,col,bus | 0.12       |

| row,bank,bus,dimm,col | 0.64       | col,bus,row,dimm,bank | 0.12       |

| row,dimm,bank,bus,col | 0.63       | col,bus,row,bank,dimm | 0.10       |

| row,bus,bank,dimm,col | 0.58       | dimm,col,bank,bus,row | 0.10       |

| dimm,row,bus,bank,col | 0.50       | row,bus,col,dimm,bank | 0.10       |

| row,dimm,bus,bank,col | 0.50       | dimm,row,bus,col,bank | 0.09       |

| bank,bus,dimm,col,row | 0.50       | row,dimm,bus,col,bank | 0.09       |

| bank,bus,dimm,row,col | 0.50       | row,bus,dimm,col,bank | 0.09       |

| bus,dimm,col,bank,row | 0.46       | row,bank,col,dimm,bus | 0.09       |

| bank,dimm,col,bus,row | 0.46       | dimm,row,bank,col,bus | 0.09       |

| dimm,bank,col,bus,row | 0.45       | row,dimm,bank,col,bus | 0.09       |

| dimm,bus,col,bank,row | 0.43       | row,bank,col,bus,dimm | 0.08       |

| bank,bus,row,dimm,col | 0.36       | col,dimm,bank,bus,row | 0.08       |

| bus,bank,col,dimm,row | 0.35 | row,bank,dimm,col,bus | 0.08 |

|-----------------------|------|-----------------------|------|

| bus,col,dimm,bank,row | 0.35 | row,bus,col,bank,dimm | 0.08 |

| bank,row,dimm,bus,col | 0.33 | col,bank,dimm,bus,row | 0.07 |

| bus,row,dimm,bank,col | 0.33 | dimm,col,bank,row,bus | 0.07 |

| row,bus,dimm,bank,col | 0.33 | col,bank,dimm,row,bus | 0.07 |

| row,bank,dimm,bus,col | 0.33 | col,bank,bus,row,dimm | 0.07 |

| bus,bank,row,col,dimm | 0.32 | col,bank,bus,dimm,row | 0.07 |

| bus,bank,col,row,dimm | 0.32 | col,dimm,bank,row,bus | 0.06 |

| bus,row,bank,col,dimm | 0.32 | dimm,col,row,bus,bank | 0.06 |

| bank,row,bus,col,dimm | 0.32 | row,dimm,col,bus,bank | 0.05 |

| row,bus,bank,col,dimm | 0.32 | col,dimm,row,bus,bank | 0.05 |

| row,bank,bus,col,dimm | 0.32 | dimm,row,col,bus,bank | 0.05 |

| bus,col,bank,dimm,row | 0.28 | col,bank,row,dimm,bus | 0.05 |

| bus,col,dimm,row,bank | 0.28 | col,bank,row,bus,dimm | 0.05 |

| bus,dimm,row,col,bank | 0.26 | dimm,row,col,bank,bus | 0.04 |

| bank,dimm,col,row,bus | 0.25 | col,dimm,row,bank,bus | 0.04 |

| bank,dimm,row,col,bus | 0.25 | row,dimm,col,bank,bus | 0.04 |

| dimm,bank,col,row,bus | 0.24 | row,col,dimm,bus,bank | 0.04 |

| dimm,bus,col,row,bank | 0.24 | col,row,dimm,bus,bank | 0.04 |

| dimm,bank,row,col,bus | 0.24 | dimm,col,row,bank,bus | 0.04 |

| dimm,bus,row,col,bank | 0.24 | col,row,dimm,bank,bus | 0.04 |

| bus,dimm,col,row,bank | 0.23 | row,col,dimm,bank,bus | 0.03 |

| bank,col,dimm,bus,row | 0.23 | row,col,bus,dimm,bank | 0.03 |

| bus,col,bank,row,dimm | 0.22 | row,col,bus,bank,dimm | 0.03 |

| bus,row,col,dimm,bank | 0.21 | col,row,bus,dimm,bank | 0.03 |

| bus,col,row,dimm,bank | 0.21 | col,row,bus,bank,dimm | 0.03 |

| bank,bus,col,dimm,row | 0.20 | col,row,bank,dimm,bus | 0.03 |

| bank,bus,row,col,dimm | 0.20 | row,col,bank,dimm,bus | 0.02 |

| bank,bus,col,row,dimm | 0.20 | row,col,bank,bus,dimm | 0.02 |

| bank,col,bus,dimm,row | 0.19 | col,row,bank,bus,dimm | 0.02 |

The DRAM controller efficiency results listed in Table 4.1 range from 93% down to 2%, demonstrating that the access ordering makes a substantial difference in effective memory bandwidth. Only 21 of the 120 access patterns achieved greater than 50% efficiency and over half of the access patterns resulted in less than 20% efficiency.

Any access pattern where the DRAM column and row were the two least frequently changed address fields achieved 92-93% efficiency, except for the following two cases which resulted in only 50% efficiency:

1. bank,bus,dimm,col,row

# 2. bank,bus,dimm,row,col

In these cases, contention for a single DIMM reduces memory performance.

The worst efficiency was observed for access patterns where row and column change the most frequently. All twelve of these access patterns resulted in less than 4% efficiency. However, Convey's scheduler was able to achieve good efficiency in some cases when the DRAM row was changed every cycle, as shown in the following cases:

- 1. row,bank,bus,dimm,col (64%)

- 2. row,dimm,bank,bus,col (63%)

- 3. row,bus,bank,dimm,col (58%)

- 4. row,dimm,bus,bank,col (50%)

- 5. row,bus,dimm,bank,col (33%)

- 6. row,bank,dimm,bus,col (33%)

The memory bandwidth test shows that the access ordering makes a substantial difference in effective memory bandwidth. To achieve high memory bandwidth, the memory should be accessed consecutively as much as possible given the specific memory access pattern of a kernel.

#### 4.2 IMPACT OF DOUBLE BUFFERING ON MEMORY LATENCY HIDING

As described in Chapter 2, double buffering is the first attempt to hide memory latency. However, double buffering introduces inefficiency in memory controller interface due to contentions of the buffers for memory accesses and kernel pipeline. To measure the inefficiency, a performance counter is used to count the number of cycles where there is no memory read or write without a corresponding memory stall request. This differentiates inefficiencies in DRAM controller with inefficiencies in the memory controller interface.

The number is then divided by the number of execution cycles to obtain the interface stall rate.

We used MrBayes kernel, a memory-bound kernel, to evaluate the inefficiency of double buffering in a memory interface design. The results in Table 4.2 shows the interface stall rate depends on the size of the each buffer. The stall rate is high for very small and very large buffers and drops when the buffer is around 1K-entry deep. The interface stall rate in double buffering leads to the pursuit of a better memory latency hiding technique. As compared to double buffering, FPGA test shows circular buffering using Convey's reorder buffer has zero interface stall rate. So all the experimental results that follow assume the memory controller interface has implemented circular buffering to eliminate the stall that arises from the inefficiency of the buffering for memory latency hiding.

# 4.3 IMPACT OF LOOP AND ARRAY ACCESS ORDERS

In order to evaluate the performance of the memory access orders, we implemented a 3D 6-point stencil loop on the Convey HC-1. Figure 4.1 shows the stencil loop kernel and Figure 4.2 shows the block diagram of the design for one PE.

The order of address generation affects the memory access pattern, which in turn affects memory performance. We define two memory access orders, *the loop order* and *the*

```

\begin{array}{l} \text{for } i{=}1 \text{ to } x{-}2 \text{ do} \\ \text{for } j{=}1 \text{ to } y{-}2 \text{ do} \\ \text{for } k{=}1 \text{ to } z{-}2 \text{ do} \\ S[i,j,k] = A[i{-}1,j,k] + A[i{+}1,j,k] + A[i,j{-}1,k] + \\ A[i,j{+}1,k] + A[i,j,k{-}1] + A[i,j,k{+}1]; \\ \text{endfor} \\ \text{endfor} \\ \text{endfor} \end{array}

```

Figure 4.1 6-point 3D stencil loop kernel

array order. In the loop order, all inputs for each loop iteration are requested before proceeding to request the inputs required by next iteration. The ordering leads to nonconsecutive accesses within each loop iteration. It is not necessary to request all inputs of one iteration before requesting all inputs of the next iteration. In the array order, all

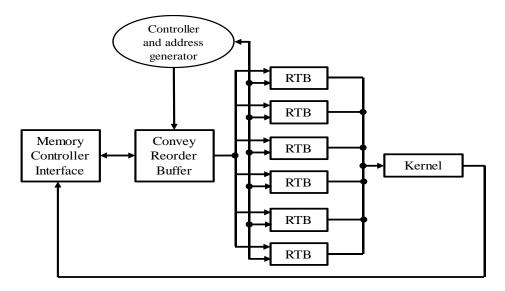

Figure 4.2 Block diagram of the 6-point 3D stencil for each PE

inputs belonging to each array are requested as needed by the iteration range covered by the buffer before moving to the next array. The ordering leads to non-consecutive access

Table 4.2 Memory interface stall rate using double buffering

| Buffer size | Interface stall rate |

|-------------|----------------------|

| 256         | 20.7%                |

| 512         | 9.3%                 |

| 1K          | 6.2%                 |

| 2K          | 10.8%                |

| 3K          | 16.1%                |

| 4K          | 20.5%                |

for each array at the boundary of iteration range. The size of the iteration range is also referred to as *block size*.

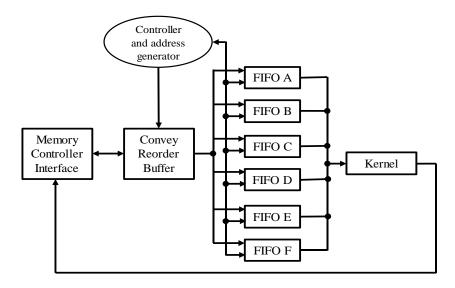

The address generator produces the memory addresses in either the loop or array order. Convey's read reorder buffer receives data requests and returns the data to the kernel through the input FIFOs. Each of six input FIFOs corresponds to one of the six elements in the 6-point stencil. When any FIFO is almost full, the read reorder buffer will stop sending data to the FIFO. When all the FIFOs are not empty, the kernel accumulates six FIFO output data in parallel. The accumulation result is then written to the memory through the memory interface.

Table 4.3 DRAM controller efficiency of 6-point 3D stencil

| Request Order | Loop | Array |

|---------------|------|-------|

| Block size    | 1    | 85    |

| Efficiency    | 67%  | 90%   |

The design is implemented using only two PEs accessing just one memory controller. Table 4.3 shows DRAM controller efficiency is 67% for the loop order and 90% for the array order. It is expected that the efficiency will be lower when 64 PEs of four AEs run in parallel. In the loop order, we request six elements in the innermost loop of the stencil code before proceeding to request the elements of the next loop iteration. In the array order, we request an array of elements of 85 iterations before proceeding to request next array of elements of 85 iterations. It is assumed that when block size is 1 the array order reduces to the loop order. Note this specific block size of 85 is only introduced as part of the

preliminary 3D 6-point stencil result. The experimental result in Chapter 6 will take block size as a parameter for studying the impact of block size on the memory performance.

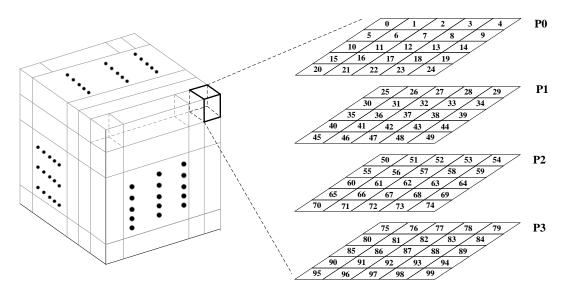

### 4.4 DATA REUSE ANALYSIS OF 3D STENCIL

In the stencil code shown in Figure 4.1, six references to the array A are located in the innermost loop of the nested loops. The references are R0 (A[i-1, j, k]), R1(A[i+1, j, k]), R2(A[i, j-1, k]), R3(A[i, j+1, k]), R4(A[i, j, k-1]) and R5(A[i, j, k+1]). An array element accessed by one reference in an iteration may be accessed again by other references in other iterations. For example, the array element accessed by reference R3 in iteration (i, j+1, k) can be reused by reference R2 in iteration (i, j+2, k).

As introduced in Chapter 2, data reuse is realized using on-chip buffers. If the size of on-chip buffers is large enough to store all elements of array A after requesting them from the memory, then all loop iterations can access the elements from the on-chip buffers, achieving maximum data reuse. If data reuse is not enabled, then each iteration has to access six elements from the memory to produce an output element. Since the size of on-chip buffers is limited, some redundant accesses are required to request the same elements that have been requested before.

We have built a FIFO-based model to analyze data reuse rate using different sizes of on-chip buffers and stencil space. The model counts the total number of reused memory references in the 3D stencil kernel loops and then divide it by the total number of memory references without data reuse to compute data reuse rate. When the FIFO buffer cannot hold a new memory reference due to the limited size, the oldest reference in the buffer is removed to provide space for storing the new reference.

Table 4.4 Data reuse rate of 6-point 3D stencil

|     | 16    | 32    | 64    | 128   | 256   | 512   | 1024  | 4096  | $N^3$ |

|-----|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| 5   | 0.148 | 0.302 | 0.500 | 0.500 | 0.500 | 0.500 | 0.500 | 0.500 | 0.500 |

| 10  | 0.125 | 0.125 | 0.411 | 0.417 | 0.69  | 0.708 | 0.708 | 0.708 | 0.708 |

| 16  | 0.143 | 0.143 | 0.154 | 0.452 | 0.452 | 0.452 | 0.452 | 0.762 | 0.762 |

| 32  | 0.156 | 0.156 | 0.156 | 0.156 | 0.478 | 0.478 | 0.478 | 0.800 | 0.800 |

| 64  | 0.161 | 0.161 | 0.161 | 0.161 | 0.161 | 0.489 | 0.489 | 0.489 | 0.817 |

| 128 | 0.164 | 0.164 | 0.164 | 0.164 | 0.164 | 0.164 | 0.495 | 0.495 | 0.825 |

| 256 | 0.165 | 0.165 | 0.165 | 0.165 | 0.165 | 0.165 | 0.165 | 0.165 | 0.829 |

| 512 | 0.166 | 0.166 | 0.166 | 0.166 | 0.166 | 0.166 | 0.166 | 0.166 | 0.831 |

Table 4.5 Data reuse rate of 27-point 3D stencil

|     | 16    | 32    | 64    | 128   | 256   | 512   | 1024  | 4096  | $N^3$ |

|-----|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| 5   | 0.198 | 0.442 | 0.689 | 0.829 | 0.829 | 0.829 | 0.829 | 0.829 | 0.829 |

| 10  | 0.259 | 0.579 | 0.583 | 0.826 | 0.826 | 0.928 | 0.928 | 0.928 | 0.928 |

| 16  | 0.275 | 0.616 | 0.619 | 0.619 | 0.855 | 0.855 | 0.945 | 0.945 | 0.945 |

| 32  | 0.286 | 0.643 | 0.644 | 0.644 | 0.644 | 0.874 | 0.874 | 0.955 | 0.955 |

| 64  | 0.292 | 0.655 | 0.655 | 0.655 | 0.655 | 0.655 | 0.882 | 0.882 | 0.959 |

| 128 | 0.294 | 0.661 | 0.661 | 0.661 | 0.661 | 0.661 | 0.661 | 0.885 | 0.961 |

| 256 | 0.295 | 0.663 | 0.664 | 0.664 | 0.664 | 0.664 | 0.664 | 0.664 | 0.962 |

| 512 | 0.296 | 0.665 | 0.665 | 0.665 | 0.665 | 0.665 | 0.665 | 0.665 | 0.963 |